-

Notifications

You must be signed in to change notification settings - Fork 1

Home

Note: This project is under heavy construction.

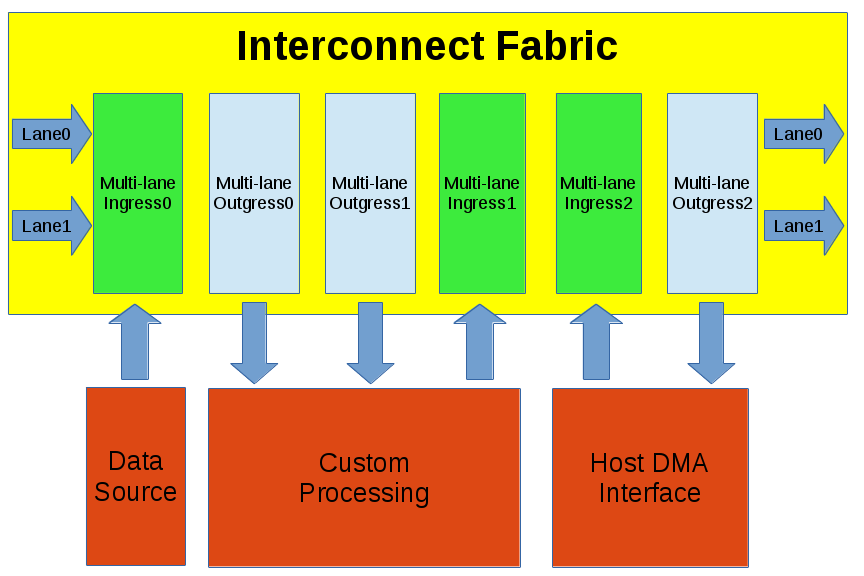

The Pothos FPGA project interfaces FPGA processing blocks with the Pothos framework and graphical tools. Multiple processing blocks and host ingress/outgress blocks may be connected to the interconnect and built into an FPGA image. The interconnect has configurable complexity such as number of high-speed lanes, port width, and number of I/Ogress ports.

The user creates a topology of processing blocks, both regular general purpose processor style blocks, and block representing processing in the FPGA. The topology determines how the interconnect in the FPGA should be configured to route the data according to the flow of connections in the topology.

- Flows between FPGA and GPP blocks will route through the host DMA blocks and make use the zero-copy buffer integration support in Pothos.

- Flows between FPGA processing blocks will route directly through the interconnect without any runtime intervention from the host computer.

Therefore, a user can dynamically configure the flow of data both inside and outside of the FPGA, and easily move data between host and FPGA, simply by expressing the desired connections to the framework.

- Unit tests get easier: A user can unit test any individual FPGA block in the design with host-driven data. We can write unit test topologies to run with live FPGA images or against simulations.

- Debugging gets easier: We can snoop-in on any given flow within the FPGA simply by connecting to it. If the data rate is too high, we can first connect a monitor block that yields output periodically or on trigger events.

It will be possible to graphically connect the interconnect IP to AXI style processing IP within the Vivado design tool. We have adaptors for APB3 peripheral bus and AXI4 stream bus.

Install GHDL for simulation:

sudo add-apt-repository ppa:pgavin/ghdl sudo apt-get update sudo apt-get install ghdl