-

Notifications

You must be signed in to change notification settings - Fork 0

Home

- Introduction

- Installation in Icestudio

- Binary Encoders

- Binary Decoders

- Translations

- Organization of the collection

- Contributing to the collection

In this collection you will find Binary Encoders and Decoders. Use these blocks in your digital circuits for opensource FPGAs created with icestudio. All the components of this collection are combinational

Find information about collections and how to install them on this link: Installing the iceK collection in Icestudio. It was written for the iceK collection as an example. Use the repo of the iceCoders collection instead

- Download the ZIP file from the latest release

- ...or get the ZIP file with the latest changes from the main branch: iceCoders.zip

The main binary Encoders are 2-to-1, 4-to-2 and 8-to-3. There are different flavours for all of them: Standard, Bus and active low inputs

All the binary encoders are built from the basic 2-to-1 Encoder, which in turn is built from logic gates. There are different flavours

The basic 2-to-1 binary encoder have two 1-bit inputs and two 1-bit outputs. These inputs correspond to a 2-bit number that we want to encode into the out output (1-bit). The other output is nz. It is used to validate the output number. If nz is active, it means that there is a valid encoded number in out

The binary codification is as follows. It assumes that there is only one active input at anytime. If the input 1 is active, the data output is 1. On the contrary, if the input 0 is active, the data output is 0. This is only valid if the nz ouptut is 1. In case none of the inputs are active, nz is 0, meaning that there is no number to encode

It can happen that both inputs, 0 and 1, are active. In that case, as the input 1 has more priority than input 0, the encoded number produced at the output is 1. This is the truth table of the Encoder 2-1:

| Input 1 | Input 0 | out | nz | Description |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | No inputs active |

| 0 | 1 | 0 | 1 | Input 0 active |

| 1 | 0 | 1 | 1 | Input 1 active |

| 1 | 1 | 1 | 1 | Input 1 active |

This example is available on the File/Examples/01-Encoder-2-1/Alhambra-II/01-Encoder-2-1-button-LED menu. It is an example of manually testing a 2-to-1 encoder with two buttons and two LEDs, for the Alhambra-II ICE40 FPGA board. The LED7 is the output. It shows the encoded number. The LED0 is the nz output. Only when this LED is on, the output is valid

The 2-to-1 Encoder is implemented from logic gates

The Encoder-2-1-verilog is exactly the same than the Encoder-2-1, but implemented directly in verilog:

This is the verilog code:

//-- 2-1 Encoder

assign out = i1;

assign nz = i1 | i0;The Encoder-2-1-bus component is exactly the same as the Encoder-2-1, but both inputs, i0 and i1 are taken from the input bus instead of from isolated wires

The Encoder-2-1-Bus is implemented with an split block connected to an Encoder-2-1

It is very common that the inputs to a binary encoder are active low (For example when connected to a buttons through a pull-up resistor). In these cases the truth table is as follows:

| Input 1 | Input 0 | out | nz | Description |

|---|---|---|---|---|

| 1 | 1 | 0 | 0 | No inputs active |

| 1 | 0 | 0 | 1 | Input 0 active |

| 0 | 1 | 1 | 1 | Input 1 active |

| 0 | 0 | 1 | 1 | Input 1 active |

Notice that the outputs have the same values. Only the inputs are negated with respect the original 2-1 encoder

There are two kinds of 2-1 enconders with active low inputs depending on how we group the inputs: 2 wires or 2-bits Bus

It is implemented with a 2-1 Enconder and two not gates connected to its inputs

It is implemented similarly, but using a 2-bits input NOT gate

Example of use of the 2-1 Encoder with active low inputs. It works exactly as the example 1, but the buttons are external (connected with pull-ups) and connected by a 2-bits bus

The 4-to-2 Binary enconder is built from 2-to-1 Encoders, which in turn are built from logic gates. There are different flavours

The basic 4-to-2 binary encoder have four 1-bit inputs and three 1-bit outputs. These inputs correspond to a 4-bit number that we want to encode into the out output (2-bits). The other output is nz. It is used to validate the output number. If nz is active, it means that there is a valid encoded number in out

The binary codification, with priority is shown on this table:

| I3 | I2 | I1 | I0 | out | nz | Description |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | No inputs active |

| 0 | 0 | 0 | 1 | 1 | 1 | Input 0 active |

| 0 | 0 | 1 | x | 1 | 1 | Input 1 active |

| 0 | 1 | x | x | 1 | 1 | Input 2 active |

| 1 | x | x | x | x | 1 | Input 3 active |

The x means "Don't care". It does not matter the x value (0 or 1). The highest priority is for the most significant bit (I3). The lowest priority for the least significant bit (I0)

This example is available on the File/Examples/03-Encoder-4-2/Alhambra-II/03-Encoder-2-4-button-LEDs menu. It is an example of manually testing a 4-to-2 encoder with one button and three LEDs, for the Alhambra-II ICE40 FPGA board. The LED7 and LED6 are the outputs. They show the encoded number. The LED0 is the nz output. Only when this LED is on, the output is valid

The switch SW1 is used for shifting the "1" bit to the other flip-flips so that the following pattern is generated in the bits a3, a2, a1 and a0: 0000, 0001, 0010, 0100 and 1000. These are the 4-bit numbers to be encoded into 2-bits

The 4-to-2 Encoder is implemented from two 2-1 enconders, one mux-2-1 and logic gates

The Encoder-4-2-verilog is exactly the same than the Encoder-4-2, but implemented directly in verilog:

This is the verilog code:

//-- 4-2 Binary encoder with priority

reg [1:0]out;

wire [3:0]y = {i3, i2, i1, i0};

always @*

begin

casex(y)

4'b0001: out = 2'b00;

4'b001x: out = 2'b01;

4'b01xx: out = 2'b10;

4'b1xxx: out = 2'b11;

default: out = 2'b00;

endcase

end

assign {o1,o0} = out;

assign nz = |y;The Encoder-4-2-bus component is exactly the same as the Encoder-4-2, but both the input number and the output encoded number are Buses instead of isolated wires

The Encoder-4-2-Bus is implemented with an split block connected to an Encoder-4-2

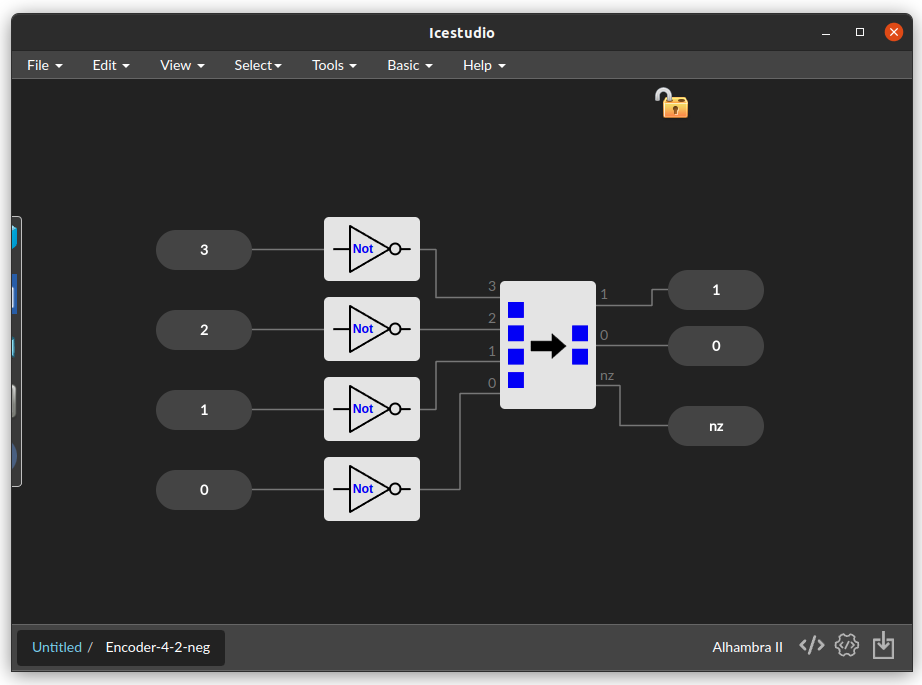

It is very common that the inputs to a binary encoder are active low (For example when connected to buttons through pull-up resistors). In these cases the truth table is as follows:

| Input 3 | Input 2 | Input 1 | Input 0 | out | nz | Description |

|---|---|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 00 | 0 | No inputs active |

| 1 | 1 | 1 | 0 | 00 | 1 | Input 0 active |

| 1 | 1 | 0 | x | 01 | 1 | Input 1 active |

| 1 | 0 | x | x | 10 | 1 | Input 2 active |

| 0 | x | x | x | 11 | 1 | Input 3 active |

Notice that the outputs have the same values. Only the inputs are negated with respect the original 4-2 encoder

There are two kinds of 4-2 enconders with active low inputs depending on how we group the inputs: 4 wires or 4-bits Bus

It is implemented with a 4-2 Enconder and four not gates connected to its inputs

It is implemented similarly, but using a 4-bits input NOT gate

Example of use of the 4-2 Encoder with active low inputs. Four external buttons are connected using pull-ups resistors (So that they work with negative logic: 1 means the button is idle, 0 if the button is pressed)

The 8-to-3 Binary enconder is built from 4-to-2 Encoders, which in turn are built from logic gates. There are different flavours

The basic 8-to-4 binary encoder have eight 1-bit inputs and four 1-bit outputs. These inputs correspond to a 4-bit number that we want to encode into the out output (3-bits). The other output is nz. It is used to validate the output number. If nz is active, it means that there is a valid encoded number in out

The binary codification, with priority is shown on this table:

| I7 | I6 | I5 | I4 | I3 | I2 | I1 | I0 | out | nz | Description |

|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 000 | 0 | No inputs active |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 000 | 1 | Input 0 active |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | x | 001 | 1 | Input 1 active |

| 0 | 0 | 0 | 0 | 0 | 1 | x | x | 010 | 1 | Input 2 active |

| 0 | 0 | 0 | 0 | 1 | x | x | x | 011 | 1 | Input 3 active |

| 0 | 0 | 0 | 1 | x | x | x | x | 100 | 1 | Input 4 active |

| 0 | 0 | 1 | x | x | x | x | x | 101 | 1 | Input 5 active |

| 0 | 1 | x | x | x | x | x | x | 110 | 1 | Input 6 active |

| 1 | x | x | x | x | x | x | x | 111 | 1 | Input 7 active |

The x means "Don't care". It does not matter the x value (0 or 1). The highest priority is for the most significant bit (I7). The lowest priority for the least significant bit (I0)

This example is available on the File/Examples/05-Encoder-8-3/Alhambra-II/05-Encoder-8-3-button-LEDs menu. It is an example of manually testing a 8-to-3 encoder with one button and three LEDs, for the Alhambra-II ICE40 FPGA board. The LEDs 7,6 and 5 are the outputs. They show the encoded number. The LED0 is the nz output. Only when this LED is on, the output is valid

The switch SW1 is used for shifting the "1" bit to the other flip-flips so that the following pattern is generated in the bits a7-a0: 00000000, 10000000, 01000000, 00100000, 00001000, 00000100, 00000010, 00000001. These are the 8-bit numbers to be encoded into 3-bits

The 8-to-3 Encoder is implemented from two 4-2 enconders, one 2-bits mux-2-1 and logic gates

The Encoder-8-3-verilog is exactly the same than the Encoder-8-3, but implemented directly in verilog:

This is the verilog code:

//-- 8-3 Binary encoder with priority

reg [2:0]out;

wire [7:0]y = {i7,i6,i5,i4,i3, i2, i1, i0};

always @*

begin

casex(y)

8'b00000001: out = 3'b000;

8'b0000001x: out = 3'b001;

8'b000001xx: out = 3'b010;

8'b00001xxx: out = 3'b011;

8'b0001xxxx: out = 3'b100;

8'b001xxxxx: out = 3'b101;

8'b01xxxxxx: out = 3'b110;

8'b1xxxxxxx: out = 3'b111;

default: out = 3'b000;

endcase

end

assign {o2,o1,o0} = out;

assign nz = |y;The Encoder-8-3-bus component is exactly the same as the Encoder-8-2, but both the input number and the output encoded number are Buses instead of isolated wires

The Encoder-8-3-Bus is implemented with an split block connected to an Encoder-8-3. Its outputs are joined into a Bus

It is very common that the inputs to a binary encoder are active low (For example when connected to buttons through pull-up resistors). In these cases the truth table is as follows:

| I7 | I6 | I5 | I4 | I3 | I2 | I1 | I0 | out | nz | Description |

|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 000 | 0 | No inputs active |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 000 | 1 | Input 0 active |

| 1 | 1 | 1 | 1 | 1 | 1 | 0 | x | 001 | 1 | Input 1 active |

| 1 | 1 | 1 | 1 | 1 | 0 | x | x | 010 | 1 | Input 2 active |

| 1 | 1 | 1 | 1 | 0 | x | x | x | 011 | 1 | Input 3 active |

| 1 | 1 | 1 | 0 | x | x | x | x | 100 | 1 | Input 4 active |

| 1 | 1 | 0 | x | x | x | x | x | 101 | 1 | Input 5 active |

| 1 | 0 | x | x | x | x | x | x | 110 | 1 | Input 6 active |

| 0 | x | x | x | x | x | x | x | 111 | 1 | Input 7 active |

Notice that the outputs have the same values. Only the inputs are negated with respect the original 8-3 encoder

There are two kinds of 8-3 enconders with active low inputs depending on how we group the inputs: 8 wires or 8-bits Bus

It is implemented with a 8-3 Enconder and eight not gates connected to its inputs

It is implemented similarly, but using a 8-bits input NOT gate

Example of use of the 8-3 Encoder with active low inputs. Four external buttons are connected using pull-ups resistors (So that they work with negative logic: 1 means the button is idle, 0 if the button is pressed)

The main binary Decoders are 1-to-2, 2-to-4 and 3-to-8. There are different flavours for all of them: Standard, Bus and active low outputs

All the binary decoders are built from the basic 1-to-2 Decoder, which in turn is built from logic gates. There are different flavours

The basic 1-to-2 binary decoder have one 1-bit input and two 1-bit outputs. The input correspond to a 1-bit number that we want to decode into the two output bits

The binary decodification is shown on this table:

| Input | Output 1 | Output 0 | Description |

|---|---|---|---|

| 0 | 0 | 1 | Output 0 active |

| 1 | 1 | 0 | Output 1 active |

Notice that there are always one output active

This example is available on the File/Examples/07-Decoder-1-2/Alhambra-II/07-Decoder-1-2-button-LED menu. It is an example of manually testing a 1-to-2 Decoder with one button and two LEDs, for the Alhambra-II ICE40 FPGA board. The LED1 and LED0 are the outputs. They show the decoded number

The 1-to-2 Decoder is implemented from logic gates

The Decoder-1-2-verilog is exactly the same than the Decoder-1-2, but implemented directly in verilog:

This is the verilog code:

//-- 1-2 Decoder

assign {01,00} = 1 << y;The Decoder-1-2-bus component is exactly the same as the Decoder-1-2, but both outputs, o0 and o1 are grouped into a Bus

The Decoder-1-2-Bus is implemented with a Decoder-1-2 and a 2-bits join block

It is very common that the outputs of a binary decoder are active low (For example when they are used for controlling a LED matrix). In these cases the truth table is as follows:

| Input | Output 1 | Output 0 | Description |

|---|---|---|---|

| 0 | 1 | 0 | Input 0 active |

| 1 | 0 | 1 | Input 1 active |

The inputs are negated with respect the original 1-2 decoder

There are two kinds of 1-2 decoders with active low outputs depending on how we group the outputs: 2 wires or 2-bits Bus

It is implemented with a 1-2 Decoder and two not gates connected to its outputs

It is implemented similarly, but using a 2-bits input NOT gate

Example of use of the 1-2 Decoder with active low outputs

The 2-to-4 Binary decoder is built from 1-to-2 decoders, which in turn are built from logic gates. There are different flavours

The basic 2-to-4 binary decoder have one 2-bits input and four 1-bit outputs. These outputs correspond to a 4-bit encoded number

The binary decodification is shown on this table:

| Input | O3 | O2 | O1 | O0 | Description |

|---|---|---|---|---|---|

| 00 | 0 | 0 | 0 | 1 | Output 0 active |

| 01 | 0 | 0 | 1 | 0 | Output 1 active |

| 10 | 0 | 1 | 0 | 0 | Output 2 active |

| 10 | 1 | 0 | 0 | 0 | Output 3 active |

This example is available on the File/Examples/09-Decoder-2-4/Alhambra-II/09-Decoder-2-4-button-LEDs menu. It is an example of manually testing a 2-to-4 Decoder with two buttons and three LEDs, for the Alhambra-II ICE40 FPGA board. The LEDs 3-0 are the outputs. They show the decoded number

The 2-to-4 Decoder is implemented from two 1-2 Decoders, four And gates and one Split block

The Decoder-2-4-verilog is exactly the same than the Decoder-2-4, but implemented directly in verilog:

This is the verilog code:

//-- Decode 2-4

assign {o3, o2, o1, o0} = 1 << y;The Decoder-2-4-bus component is exactly the same as the Decoder-2-4, but the output is a Bus instead of isolated wires

The Decoder-2-4-Bus is implemented with an Decoder-4-2 and a join block

It is very common that the outputs of a binary decoder are active low. In these cases the truth table is as follows:

| Input | o3 | o2 | o1 | o0 | Description |

|---|---|---|---|---|---|

| 00 | 1 | 1 | 1 | 0 | Output 0 active |

| 01 | 1 | 1 | 0 | 1 | Output 1 active |

| 10 | 1 | 0 | 1 | 1 | Output 2 active |

| 11 | 0 | 1 | 1 | 1 | Output 3 active |

There are two kinds of 2-4 deconders with active low outputs depending on how we group the outputs: 4 wires or 4-bits Bus

It is implemented with a 2-4 Decoder and four not gates connected to its outputs

It is implemented similarly, but using a 4-bits input NOT gate

Example of use of the 2-4 Decoder with active low outputs

The 3-to-8 Binary Decoder is built from 2-to-4 decoders, which in turn are built from logic gates. There are different flavours

The basic 3-to-8 binary decoder have one 3-bits input and eight 1-bit outputs. These outputs correspond to a 8-bit encoded number

The binary decodification is shown on this table:

| Input | O7 | O6 | O5 | O4 | O3 | O2 | O1 | O0 | Description |

|---|---|---|---|---|---|---|---|---|---|

| 000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | Output 0 active |

| 001 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | Output 1 active |

| 010 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | Output 2 active |

| 011 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | Output 3 active |

| 100 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | Output 4 active |

| 101 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | Output 5 active |

| 110 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | Output 6 active |

| 111 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Output 7 active |

This example is available on the File/Examples/11-Decoder-3-8/Alhambra-II/11-Decoder-3-8-button-LEDs menu. It is an example of manually testing a 3-to-8 Decoder with one button and eigth LEDs, for the Alhambra-II ICE40 FPGA board. The LEDs 0-7 are the outputs. They show the decoded

The 3-to-8 Decoder is implemented from one 1-2 decoder, one 2-4 decoders, two Ang gates and two split blocks

The Decoder-3-8-verilog is exactly the same than the Decoder-3-8, but implemented directly in verilog:

This is the verilog code:

//-- Decode 3-8

assign {o7,o6,o5,o4,o3, o2, o1, o0} = 1 << y;The Decoder-3-8-bus component is exactly the same as the Decoder-3-8, but both the input number and the output encoded number are Buses instead of isolated wires

The Decoder-3-8-Bus is implemented with a Decoder-3-8 and a join block

It is very common that the outputs of a binary decoder are active low. In these cases the truth table is as follows:

| Input | o7 | o6 | o5 | o4 | o3 | o2 | o1 | o0 | Description |

|---|---|---|---|---|---|---|---|---|---|

| 000 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | Output 0 active |

| 001 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | Output 1 active |

| 010 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | Output 2 active |

| 011 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | Output 3 active |

| 100 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | Output 4 active |

| 101 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | Output 5 active |

| 110 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | Output 6 active |

| 111 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | Output 7 active |

There are two kinds of 3-8 decoders with active low outputs depending on how we group the outputs: 8 wires or 8-bits Bus

It is implemented with a 3-8 Decoder and eight not gates connected to its outputs

It is implemented similarly, but using an 8-bits input NOT gate

Example of use of the 3-8 Decoder with active low outputs

The collection can be translated to any language. Any translation is very welcome!! 😀️ If you want to translate it to your native languaje please follow these instructions: Translating the collection into your language. This instructions are for the iceK collection, but the translation procedure is the same for any other collection

The Organization of this collections is exactly the same than all the other collections. It consist of the following folders:

-

blocks: This is were the icestudio blocks are located, with all the elements of the collection, organized by subfolders -

examples: Circuit examples ready to use in Icestudio. Inside this examples there are some special elements:-

00-Index.ice: Collection index. Here you will see some of the more important blocks that the collection contains -

TESTs: This is used by the collection developer for testing the different blocks. Everytime a block is added, it should be tested somehow. That tests are in that folder. This is not likely for the standar user, so you can skip it

-

-

icons: Here you will find the SVG files for the icons used in the collection blocks. You can edit them or create new icons from them-

block+icon: Some of the blocks in SVG, for using them in your documentations. These are some examples:

-

-

locale: Folder with the English texts and their translation into other languages -

wiki: Images used in this wiki

This is the Index file:

- 00-Index.ice:

Contributions are welcome! 😀️

You can contribute in different manners:

- Adding new blocks

- Translating the collection to your language

- Migrating the examples to more boards

These are the steps to follow for contributing:

- Fork the iceCoders repo into your github account

- Clone it to your computer

- Install the collection as an external collection, so that you can access it from icestudio (See: Other uses: External collection)

- Create your own block

- Save it and click on Tools/Collection/Reload for using it and testing it

- Commit and push to your repo

- Emit a pull request

-

The main language is English: Create all your blocks and examples in English (the English text should be inside de .ice files). Then translate it to your local language (if you like), following the instructions mentioned here: Translating the collection into your language

-

The iceCoders collection is ONLY FOR BINARY ENCODERS/DECODERS. If you want to contribute with other type of blocks, do it in its corresponding collection (iceK, iceGates, iceRegs, iceFF....)